Boot mode of TMS320F2823x/2833x at reset is decided based on the pin status of four pins.

|

MODE |

GPIO87 |

GPIO86 |

GPIO85 |

GPIO84 |

Boot mode |

|

F |

1 |

1 |

1 |

1 |

Jump to Flash |

|

E |

1 |

1 |

1 |

0 |

SCI-A boot (RAM boot) |

|

D |

1 |

1 |

0 |

1 |

SPI-A boot |

|

C |

1 |

1 |

0 |

0 |

I2C-A boot |

|

B |

1 |

0 |

1 |

1 |

eCAN-A boot |

|

A |

1 |

0 |

1 |

0 |

McBSP-A boot |

|

9 |

1 |

0 |

0 |

1 |

Jump to XINTF x16 |

|

8 |

1 |

0 |

0 |

0 |

Jump to XINTF x32 |

|

7 |

0 |

1 |

1 |

1 |

Jump to OTP |

|

6 |

0 |

1 |

1 |

0 |

Parallel GPIO I/O boot |

|

5 |

0 |

1 |

0 |

1 |

Parallel XINTF boot |

|

4 |

0 |

1 |

0 |

0 |

Jump to SARAM |

|

3 |

0 |

0 |

1 |

1 |

Branch to check boot mode |

|

2 |

0 |

0 |

1 |

0 |

Branch to Flash, skip ADC calibration |

|

1 |

0 |

0 |

0 |

1 |

Branch to SARAM, skip ADC calibration |

|

0 |

0 |

0 |

0 |

0 |

Branch to SCI, skip ADC calibration |

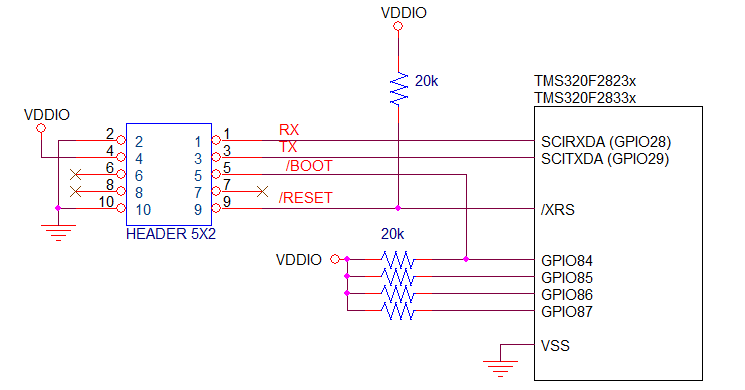

easyDSP activates both /BOOT and

/RESET pins low for RAM booting. It activates only /RESET pin low for the

menu 'DSP>Reset DSP'.

An easyDSP uses either ‘Jump to Flash’ mode or ‘SCI-A boot’ by setting GPIO84

pin as 1 or 0 while other three pins are fixed to 1. Therefore below circuit configuration is

recommended.

- power pin (#4) of

easyDSP 5x2 header should be connected to 3.3V

- TX/RX

pins are directly connected to MCU

pins

- In case

there is a reset IC between easyDSP /RESET and MCU /XRS, it should transfer

easyDSP /RESET signal to MCU /XRS within 0.5sec

- In case you insert buffer IC between easyDSP

header and MCU, place buffer IC directly to easyDSP header so that all resistors

can be connected to directly MCU

- /RESET pin is connected to

reset generation circuit of MCU

board

(Time duration of /Reset pin is around 500msec)

- In case you use pull-up resistor to each pin, the value

of pull-up resistor should be higher than a few kilo ohm since there is 100Ω

series resistor inside easyDSP pod

- Refer to

here

for BOOT pin

operation mode.

Please be careful when you use

your own pull-up or pull-down resistor on the easyDSP signal pins. Please use

appropriate filter circuit to your reset generation circuit to prevent

unintentional reset generation.